The relentless pursuit of computational efficiency has long been haunted by a formidable bottleneck known as the "memory wall." This term describes the critical performance limitation that arises from the physical separation between the central processing unit (CPU) and main memory in conventional von Neumann architectures. Data must constantly shuttle back and forth across this divide, a process that consumes immense amounts of time and energy. As processors have become exponentially faster, this data movement has emerged as the dominant constraint, throttling system performance and inflating power consumption, particularly for data-intensive workloads like artificial intelligence and big data analytics.

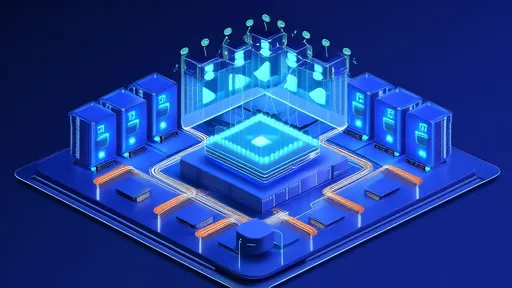

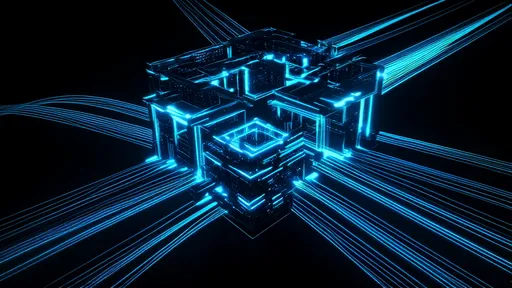

In-Memory Computing (IMC) has surged to the forefront as a revolutionary architectural paradigm poised to dismantle this wall. Unlike traditional computing, which treats memory as a passive storage repository, IMC fundamentally reimagines the relationship between data and computation. The core premise is elegantly powerful: perform computation directly within the memory array where the data resides, thereby eliminating or drastically reducing the need for costly data transfers. This is not merely an incremental improvement but a foundational shift, moving computation to the data instead of moving data to the computation.

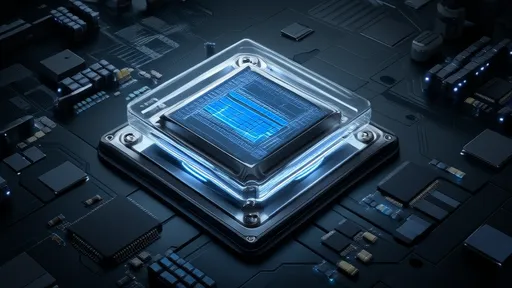

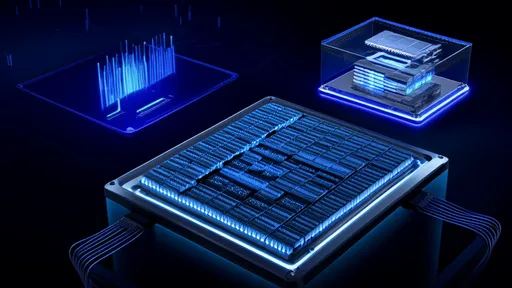

The principle behind this architecture leverages the physical properties of memory cells. By slightly modifying the peripheral circuitry of a memory array—be it SRAM, DRAM, or a non-volatile memory like Resistive RAM (ReRAM) or Phase-Change Memory (PCM)—it becomes possible to execute certain computational tasks in place. For instance, a key operation in neural networks, vector-matrix multiplication, can be performed by applying voltages to rows of a crossbar array of resistive memory devices and reading the resulting currents from the columns. This operation, which is incredibly energy-intensive in a CPU, is executed in a single step within the memory, achieving unparalleled parallelism and efficiency.

The implications for artificial intelligence are nothing short of transformative. The training and inference of deep learning models are dominated by these vast multiply-accumulate (MAC) operations. In-Memory Computing architectures, often implemented as analog compute-in-memory, can perform thousands of these operations simultaneously within a single memory block. This parallel processing capability slashes latency and can improve energy efficiency by orders of magnitude compared to shuttling data to a distant GPU or TPU. It effectively creates a highly specialized, ultra-efficient engine for the most demanding AI tasks, paving the way for more complex models to run on edge devices with severe power constraints.

Beyond AI, the data-centric nature of modern computing makes IMC a compelling solution across the spectrum. Database operations, which involve scanning, filtering, and aggregating large datasets, can be dramatically accelerated. Imagine a database query where the comparison and selection operations are performed simultaneously across entire columns of data stored in memory, instead of fetching each element sequentially to the CPU. This could revolutionize real-time analytics, financial modeling, and scientific simulations, where the speed of insight is directly tied to the speed of data access and manipulation.

The realization of this technology hinges on advancements in both memory devices and integrated circuit design. Researchers are exploring a diverse palette of emerging non-volatile memory technologies. Resistive RAM and Magnetoresistive RAM (MRAM) are particularly promising candidates due to their high density, endurance, and ability to precisely modulate their resistance states, which can directly represent synaptic weights or numerical values. The integration challenge is immense, requiring co-design of the memory arrays, the modified sense amplifiers that read computational results, and the digital logic that manages the flow of operations, all without compromising the density or yield of the memory itself.

Despite its profound potential, the path to widespread adoption of In-Memory Computing is strewn with challenges. Precision and accuracy remain significant hurdles for analog implementations; device variations, noise, and resistance drift can introduce errors into computations. Sophisticated error correction codes, algorithmic adjustments, and hybrid digital-analog schemes are under active development to mitigate these issues. Furthermore, IMC is currently not a general-purpose replacement for von Neumann architectures. It excels at specific, highly parallel tasks but is ill-suited for the complex control logic and branching operations that CPUs handle well. The future likely lies in heterogeneous systems that intelligently partition workloads between traditional cores and IMC accelerators.

The industry landscape is already buzzing with activity. Major semiconductor companies and ambitious startups alike are pouring resources into developing and commercializing IMC solutions. Some are focusing on near-term integration with existing CMOS technology, creating SRAM-based IMC macros for AI accelerators. Others are betting on the long-term prospects of novel resistive memories to create denser, more efficient systems. Prototype chips are demonstrating staggering efficiency gains, and the first commercial products targeting AI inference in smartphones and sensors are beginning to emerge, signaling the transition from laboratory curiosity to tangible technology.

In-Memory Computing represents more than just a new chip design; it is a fundamental rethinking of how we compute in an era defined by data. By collapsing the traditional hierarchy and fusing memory and processing, it attacks the very heart of the memory wall problem. While technical obstacles remain, the trajectory is clear. As the architecture matures and overcomes its precision and integration challenges, it is poised to unlock unprecedented levels of performance and efficiency, fueling the next generation of intelligent machines and data-driven discoveries. The walls are beginning to crumble.

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025

By /Aug 26, 2025